- SK Hynix introduce la tecnología 'multi-site cell' para aumentar la densidad de las SSD.

- Este método divide las celdas de memoria para almacenar 5 bits, mejorando la fiabilidad y velocidad.

- La nueva tecnología podría hacer viable la memoria flash de 5 bits, aunque no abaratará los SSD.

La industria de la memoria flash busca constantemente formas de incrementar la densidad de almacenamiento para satisfacer la creciente demanda de centros de datos, dispositivos de consumo y herramientas de inteligencia artificial. El escalado convencional mediante capas adicionales de 3D NAND se ha vuelto cada vez más complejo, costoso y difícil de fabricar de manera consistente. Si bien la memoria QLC (4 bits por celda) ya está en producción comercial, el salto a la memoria PLC (5 bits por celda) se ha mantenido poco práctico debido a problemas de fiabilidad y resistencia ligados a los límites de detección de voltaje. Sin embargo, SK Hynix ha introducido un enfoque diferente que podría cambiar este panorama.

La clave: memoria flash 'split-cell' de 5 bits

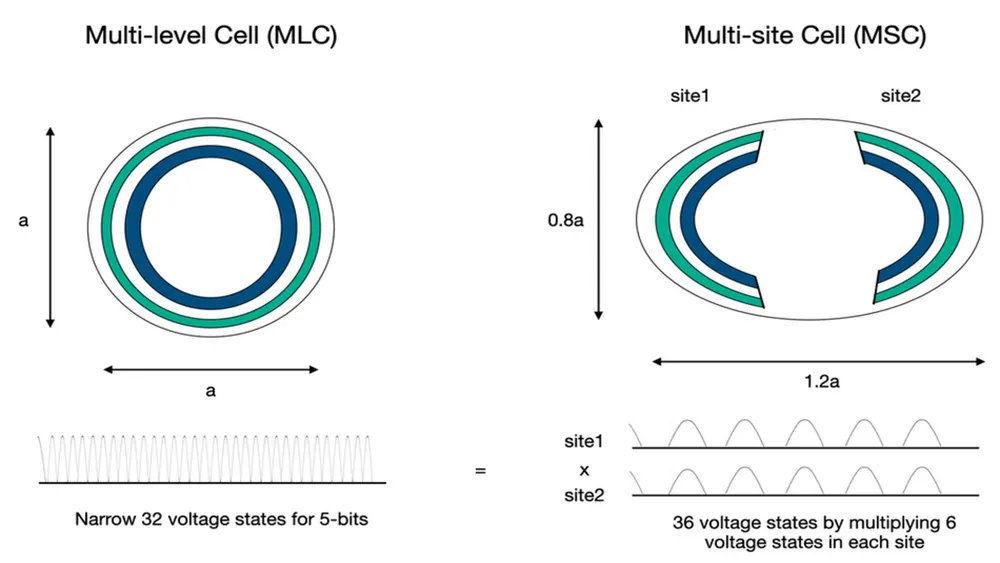

SK Hynix ha presentado un enfoque innovador conocido como tecnología 'multi-site cell'. En lugar de obligar a una única celda NAND a almacenar los 32 estados de voltaje necesarios para 5 bits, el diseño divide la celda en dos 'media celdas' independientes. Cada media celda almacena seis estados de voltaje, que se combinan para representar un valor de cinco bits. Este diseño reduce la 'congestión de voltaje' mientras mantiene la densidad de bits general. Las dos medias celdas operan en paralelo como una única unidad lógica, de forma similar a como RAID-0 distribuye datos entre discos duros para aumentar el rendimiento. En este caso, los estados de voltaje se combinan durante el acceso en lugar de distribuirse entre dispositivos separados. La forma física de la celda es elíptica, permitiendo un muro aislante entre las mitades y conexiones de línea de bits separadas.

Ventajas en velocidad y resistencia

Según SK Hynix, las mayores brechas de voltaje dentro de cada media celda reducen la fuga de electrones y acortan el tiempo de programación. Las dos mitades se leen simultáneamente, lo que, según la compañía, ofrece velocidades de lectura más rápidas en comparación con los diseños PLC convencionales. Este método también mejora la resistencia, ya que un menor estrés de voltaje reduce el desgaste de la celda. SK Hynix demostró prototipos funcionales en la conferencia IEDM de 2025, lo que indica que el concepto va más allá de la simulación. Este avance podría ser crucial para la próxima generación de unidades SSD de alta capacidad y rendimiento. Para aquellos interesados en el futuro del almacenamiento, es importante considerar cómo los avances tecnológicos como este podrían influir en el mercado, similar a como algunos SSD pueden autodestruirse.

Desafíos y futuro de las SSD de alta densidad

El enfoque 'split-cell' requiere pasos de procesamiento de semiconductores adicionales, incluyendo la división de celdas y el relleno de huecos, lo que añade coste y complejidad. Si bien SK Hynix está evaluando la viabilidad de su fabricación, se espera que otros fabricantes de memoria flash, como Samsung, Micron, Kioxia y Sandisk, estudien ideas similares. El concepto no promete SSD más baratas, sino únicamente más densas, y no elimina la necesidad de discos duros para el almacenamiento de gran capacidad. Si los fabricantes logran producir celdas 'multi-site' a escala, la memoria PLC podría finalmente ser viable sin los graves inconvenientes observados en diseños anteriores. Este desarrollo es crucial para seguir el ritmo de la demanda de almacenamiento, especialmente en áreas como la inteligencia artificial, que impulsa la necesidad de mayor capacidad y rendimiento, como se ha visto en el contexto de las exportaciones de chips de alto rendimiento. La innovación en almacenamiento, como la que podría traer la tecnología 'split-cell', es clave para mantener el avance tecnológico, junto a otros avances como el desarrollo de nuevos dispositivos móviles que requieren una mayor capacidad de almacenamiento.